Tuesday, October 5th, 2010

The mask making community, comprising the BACUS technical group of SPIE, has had a fraught relationship with maskless lithography. On the one hand, the most lucrative part of the mask-making business would vanish if massively parallel e-beam direct-write (EbDW) lithography displaced DUV or EUV to take over the leading edge. On the other hand, before that happened, the difficulty and cost of mask-making would drop precipitously, motivating an expansion in the number of designs and hence mask sets. The 2010 BACUS/SPIE Symposium on Photomask Technology in Monterey, CA, held an all-day session evaluating the prospects of Maskless Lithography on September 15.

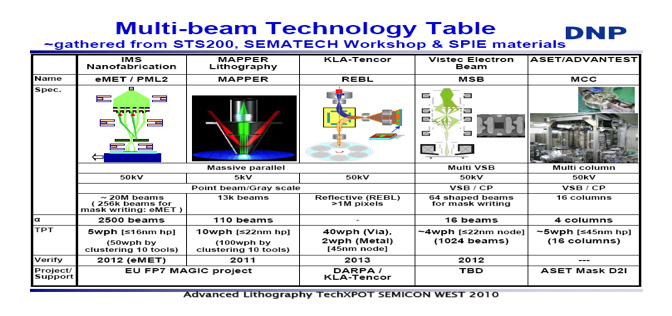

The prospects are not great, even for a limited role in prototyping or line-end cutting for gridded chip designs. Stefan Wurm of SEMATECH summarized the difficulty: maskless is not on track for insertion at the 22nm node. Full system demonstrations at specified resolution and throughput would need to be on the horizon right now. Instead, there are a variety of pre-alpha prototypes illustrating the difficulties of a massive technology shift (figure). Rather than insertion into high-volume manufacturing, Wurm advocated an application of massively parallel e-beam technology in mask-writing. Even that, however, would require an investment of $300M or so that the industry does not have available.

The prospects are not great, even for a limited role in prototyping or line-end cutting for gridded chip designs. Stefan Wurm of SEMATECH summarized the difficulty: maskless is not on track for insertion at the 22nm node. Full system demonstrations at specified resolution and throughput would need to be on the horizon right now. Instead, there are a variety of pre-alpha prototypes illustrating the difficulties of a massive technology shift (figure). Rather than insertion into high-volume manufacturing, Wurm advocated an application of massively parallel e-beam technology in mask-writing. Even that, however, would require an investment of $300M or so that the industry does not have available.

Tor Sandstrom of Micronic Laser Systems discussed two unaddressed problems: the bandwidth needed to send data into a writer capable of printing a practical number of wafers, and the need for 100% functional inspection because of the finite probability of isolated data transfer errors. To print 100 wafers-per-hour at the 16nm node, Sandstrom estimated that the pixel transfer rate would have to be 160 terapixels/second (Tp/s) for gray-scale writing or 420 Tp/s for binary writing. That corresponds to 150 times the data processing capacity of the Large Hadron Collider in Geneva, or a large building full of top-of-the-line Cisco routers, or ~10 million HDTV channels! As amazing as that demand may seem, it is theoretically within the capability of today’s fiber optics.

With any plausible bit error rate, there would be anomalies somewhere on every chip, necessitating inspection. However, what do you inspect? A real-time data driven system has vastly more defect modes than today’s DUV printing with perfect masks. Statistical inspections will not do, only full functional tests would be reassuring, and that is impossible, according to Sandstrom. Some means of multiple writing, voting and error reporting has to be implemented, complicating the system and slowing throughput. “Maskless lithography is not for the faint hearted,” summarized Sandstrom.

Neil Berglund of the Northwest Technology Group analyzed costs under various throughput conditions and found some niches where maskless lithography might be economical. However, he pointed out that in a massively parallel e-beam system, every beam had to work the same all the time. If there were more than one exposure tool, the difficulty of perfect tool matching would require “lot-to-tool dedication” where every exposure on a lot of wafers would be made on the same tool. The logistics of that would extract a cycle time penalty that might overwhelm any mask-less advantage.

The developers of massively parallel e-beam write tools all reported progress, with MAPPER (which has delivered two 110-beam pre-alpha tools to strategic customers) probably furthest along towards manufacturing. However, Bert Kampherbeek, VP of Systems Engineering at MAPPER, was fully aware of the challenges remaining. The goal remains a 10 wph tool at a cost below 5 million Euros and a footprint of 1 m2, to allow clustering. Getting there means getting all 13,000 beams up, boosting the total beam current to 160 uA on the wafer, rather than today’s picoamps, and lots of system integration.

Mark McCord of KLA-Tencor revealed breakthroughs made in their DARPA-supported reflective e-beam lithography (REBL) tool which uses a reflective pattern generator chip rather than a transmissive MEMS blanker array. KLA-Tencor has replaced the massive “magnetic prism” which separated the source and patterned beams with an elegant Wien filter and placed a channel plate micro-lens array next to the pattern generator chip to deal with fringing fields. The net result was to shorten the e-beam column to ½ meter, which allows 2.75 uA to be delivered to the chip at <45nm resolution. The 50kV, 62.5X demagnification architecture images 8 pattern generator pixels on each wafer pixel, reducing the effects of errors and anomalies. The pattern generator chip has a 248×4096 pixel array on a 1.6 um pitch, each pixel controlled by 11 transistors. Six wafers are printed simultaneously using a million beams on a continuously rotating maglev stage, with the pattern generator image following the motion of the wafers. Printing with 32 grey-scale levels allows proximity correction as well as on-the-fly error correction. The pixel pitch of 26nm has been resolved, suggesting that the DARPA goal of 45nm resolution is within reach. However, the industry needs 16nm and >10 wph. Because of Coulomb’s law, tightening resolution in e-beam lithography implies reducing beam current and throughput. Still, adding more pixels or columns could take the innovative REBL architecture far enough.

Other vendors described less radical options. Matthias Slodowski of Vistec promoted their multi-shaped beam (MSB) system. This scheme leverages the standard variable shaped beam (VSB) architecture where a flood electron beam is steered through two rectangular apertures which shape it to produce various rectangular geometries in the exposure. Vistec’s evolutionary proposal is to replace each pair of apertures with an 8×8 array, with 64 beamlets steered and shaped independently. A proof of lithography tool has worked with 16 beamlets to pattern 45nm node contact arrays. That could be enough for mask making. Akio Yamada of Advantest described their cell-projection direct write system, which is already being used in the short-turn around wafer shuttle program. With proper design for e-beam (see previous eBeam Intiative article), such systems could form a bridge to whatever comes after 32nm.

An audience member from a major semiconductor manufacturer lamented the dis-integrated and under-funded nature of the maskless lithography effort. His company wanted to use maskless lithography, but needs several complete manufacturing systems, not a bunch of disconnected projects on beam-shaping, data path, verification, etc. Established semiconductor equipment manufacturers need to take over the field and deliver qualified systems to customers, in his opinion. Big companies need two reliable sources of such critical equipment, but he did not yet see two capable companies stepping up. Without semiconductor equipment industry buy-in, the best outcome would be some orphan prototype tools, which might be tried at a few major mask companies or R&D consortia. That would not lead to a solution to the coming crisis for innovative companies and short production run chips. – M.D.L.

Tags: 22nm, BACUS, DUV, EbDW, IC, litho, lithography, MAPPER, mask, R&D, REBL, SPIE