Monday, March 21st, 2011

The 2011 SPIE Advanced Lithography Symposium was noticeably different from previous meeting which highlighted new tools and methods. This year few hardware or software tools were innovative enough to be news worthy, rather it was all about materials and the remarkable things they could be made to do – or not do.

The two inventors of the alternating phase-shift mask (alt-PSM) review a poster during SPIE AL 2011. Prof. Masato Shibuya (left) now of the Tokyo Institute of Polytechnics in Atsugi and formerly of Nikon shows his poster presentation to Dr. M. David Levenson (right) now of BetaSights and formerly of IBM. (source: SPIE)

Chip production has reached the practical limit of a single exposure of 193nm wavelength ArF immersion lithography. Going beyond with 193i exposure requires double-patterning (DP) and materials innovation, whether for the sidewall depositions in self-aligned double patterning (SADP), or for the convenient fixing of the initial photoresist pattern in multiple resist exposure methods (litho-etch-litho-etch “LELE”), or for something even more remarkable like directed self-assembly (DSA).

There was a separate conference devoted to the long hoped-for Extreme-Ultra-Violet Lithography (EUVL) production technology which would use 13.5nm exposure wavelength, but it has become clear that – for all the progress that EUVL has made and continues to make – it may not be ready for insertion before the 10nm node.

So, if the industry is going to make 10nm CD chips, it will have to be done with 193nm light – a wavelength 19X larger than the minimal feature size. The fact that the industry is contemplating such extreme sub-resolution lithography – at all – shows remarkable confidence in innovative materials and processes. Then, when the first EUV lithography tools arrive in the fab, they will be used with Resolution-Enhanced Technology (RET) since the nominal feature size will still be smaller than the exposure wavelength!

Plenary Highlights

Luc Van den hove, President and CEO of IMEC, recognized this new reality and the societal imperative for continued innovation in the first plenary presentation. We have become people of bits and bytes, according to Van den hove, communicating with everyone and everything using semiconductors in an amazing world – when it all works. Keeping it working requires continued scaling beyond the limits of ordinary silicon, planar chip designs, and DUV exposure. Van den hove foresaw the use of germanium and III-V materials in ~10nm chips and then a switch to tunnel junction transistors and 3D. Optical interconnects would speed I/O removing one present performance limit.

Of course the infrastructure to manufacture these amazing new chips has to be researched and developed now. Van den hove announced that IMEC had received the 20 truckloads from Veldhofen that would be reassembled into its NXE 3100 EUV scanner. That tool had passed qualification tests at ASML, printing 24nm line/space arrays and 26nm contact holes using dipole EUV illumination. For 15nm node production, Van den hove foresaw the use of similar EUV tools in a double patterning regime!

In his plenary talk, Shang-Yi Chiang, senior vice president of R&D at TSMC warned about the cost of all of this innovative production. He expressed the belief that ArF immersion lithography would prove too expensive beyond the 20nm node, but that there was hope that EUVL, multi-beam EbDR or some combination would prove economically viable. However, cost reductions elsewhere – perhaps through automation and a move to 450nm wafers around 2016 – would also be needed to make the new technologies competitive with the old.

Advances in Resist & Processing

Three keynotes highlighted the challenges and opportunities for the materials that register patterns on wafers in this new era. Patrick Naulleau, Interim Director of the Center for X-ray Optics at Lawrence Berkeley Laboratories (LBL), reviewed the progress (or lack thereof) in EUV resists. A viable resist must combine sufficient resolution, high sensitivity, and low Line Edge Roughness (LER) – and so far, none have done so, according to Naulleau. Progress with conventional Chemically-Amplified Resist (CAR) has stalled, possibly for fundamental reasons, whereas a non-CAR resist has shown 15nm resolution at 70mJ/cm2 sensitivity.

LER is a knotty problem, said Naulleau, with some of it coming from the mask, some from the resist-wafer interface, and some from resist exposure and development statistics. A LBL experiment found 3.4nm of correlated LER on multiple exposures of the same slightly out-of focus mask location. That result was attributed to the ~1nm reticle substrate roughness behaving like a noisy pure phase mask instead of a plane reflector. To get to 1nm LER, Naulleau predicted that 80mJ/cm2 sensitivity would have to be tolerated, and the aerial image contrast raised above 80% with perfectly flat mask substrates.

Bill Hinsberg, late of the IBM Almaden Research Center, described the lab-to-fab transition underway for DSA. In this process, phase-separation converts special block co-polymer films into technologically useful patterns as directed by topographic or chemical features imprinted on the substrate. The self-assembled structures can have a finer pitch than any conventional lithographic technique. The trick is to get the desired shapes without defects, and properly registered to whatever has been pre-patterned below. Hinsberg cited some examples from the conference and pointed out that there were broad opportunities for future materials and process development.

James Thackeray of Dow Electronic Materials then reviewed the continuing progress in materials targeted for sub-20nm lithography, which likely will be in pilot production at some NAND fab before the next conference. The Line Width Roughness (LWR) of CAR can be reduced by attaching the photo-acid generator (PAG) moiety to the polymer so as to prevent aggregation, he reported. This technique also reduces resist outgasing during exposure, preventing EUV optics contamination. CAR resist chemistry is extremely adaptable, and can meet the challenge of EUV and sub-20nm device production, averred Thackeray. He did not say it would be easy or profitable.

Negative Tone Development

Several sessions explored one remarkable example of CAR resist adaptability, negative tone development. The earliest industry photoresists were negative tone materials in which light exposure caused polymers to crosslink and become insoluble, but were entirely replaced by positive tone resists where exposure increased the rate of dissolution in an aqueous base. The problem when pushing resolution limits with negative tone resist is that the crosslinked polymers are insoluble, but absorb solvent and swell in all directions, as describe by Christopher Ober of Cornell University. This prevents good CD control and converts straight resist lines into wavy serpentines, unusable in electronics.

A more fundamental limit for positive resists, however, is that the dimensions of dissolved-away features (such vias and trenches) are limited by the wavelength of light. Negative resist would be desirable to print such features since the dimensions of dark features can be arbitrarily small, in principle (i.e. there is no wavelength of darkness).

When conventional CAR resists are developed in non-polar organic solvents instead of aqueous base, they become negative tone. The reason, according to Ober, is that the acid-catalyzed de-protection of carboxyl groups on the resin makes that material highly polar and insoluble in non-polar solvents. In aqueous base developers, those carboxyl groups enhance the solubility, exactly the opposite effect, with the result that only the unexposed hydrophobic material remains on the wafer. So, it turns out that solvent development can make yesterday’s positive CAR resist negative, a fact that has apparently been forgotten since Apex-E replaced t-BOC in the early 1980’s. In addition, the LER is reduced because of the greater optical and solubility contrast.

Several subsequent speakers elaborated on the use of negative tone developers (NTDs) which are typically non-polar organic solvents like n-heptanone or anisol-ketone mixtures. All these developers cause some thickness loss in the exposed regions and all require special handling for safety and health reasons. According to Charles Pieczulewski of Sokudo, that is now being done in production with separate stand-alone development stations for the layers requiring NTD. Young Bae of Dow reported trenches down to 40nm HP (using a topcoat-free resist) with 193i exposure at 1.35NA and aggressive dipole illumination. Shinji Tarutani of Fujifilm reported contact hole patterns down to 38nm half-pitch (with crossed-grating double exposure) and a defect density of 0.06/cm2.

A considerable number of fundamental and practical issues remain unresolved and may prove to depend on the specifics of the polymer and developer employed. For example, Stewart Robertson of KLA-Tencor reported that current resist models absolutely forbid the large experimentally measured NTD exposure latitudes. Still, whatever the models say, it is clear that for trench and contact resist, darkness and negativity are back!

Spacer Double Patterning

Low temperature atomic layer deposition (ALD) SiO2 facilitates SADP with a variety of core materials, including photoresist, according to Hidetami Yaegashi of TEL. Such flexibility reduces the number of steps and costs in pitch splitting, according to Yaegashi. For example, a self-aligned quadruple patterning (SAQP) to 11nm HP takes only 7 steps! Yaegashi predicted self aligned double patterning (SADP) would be cheaper than EUVL at 22nm unless the EUVL stepper throughput was >100wph. SADP processes can also produce the registration layers need for further pitch splitting by DSA. Koutaro Sho of Toshiba seconded the idea of depositing SiO2 over resist cores, but advocated a separate slimming process instead of over-exposure or over-development.

Other multiple deposition and selective etch processes lead to ever finer and more exotic structures. For example, TEL and Dennis Hsu of Nanya Technology revealed similar processes to fabricate <30nm contact arrays that begin with a square array of pillars that are sidewall coated just enough to leave empty space in the centers of the squares. Etching away the pillars and through the spaces transferred a ~40nm pitch split contact pattern to the wafer.

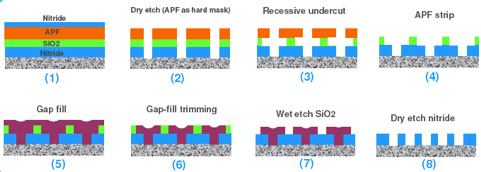

Recessive Self-Aligned Double Patterning (RSADP) process flow shown in cross-sectional schematics. (source: Applied Materials)

Other multiple patterning options (figure) were presented by Christopher Bencher and colleagues from Applied Materials in oral and poster papers at both the resist and optical lithography meetings. The key point made by Bencher was that the role of lithography has changed to generating a mandrel (a core or pre-pattern) around which patterns will be fabricated with various degrees of density multiplication. Thus it is no longer the exposure process that matters; it is the subsequent deposition and etches.

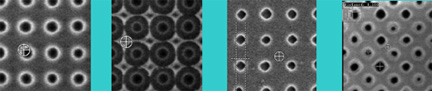

Recessive Self-Aligned Double Patterning (RSADP) results for contact holes density doubling to 50nm half pitch. (source: Applied Materials)

Applied Materials supports various mandrel, sidewall, hard-mask, and sacrificial layer material depositions that can be etched with various degrees of selectivity or isotropy to fabricate the desired result. Self-aligned double-, triple-, and quadruple-patterning can fabricate complex poly and metal layer structures for 15nm node logic. Yijian Chen, and a team from the Mayden Center highlighted the use of the different etch properties of a-Si, poly-Si, a-C, oxide, and nitride for such processes. Among the more daring variants is the recessive SADP (RSADP) process, which can be elaborated using additional materials for triple and quadruple splitting. Etch steps 2-4 and 6-7 can be combined into single recipes, and the flow can create contact holes (figure). Obviously, more development is required of this new paradigm.

Directed Self Assembly (DSA)

Complex organic materials have been assembling themselves into potentially useful structures since before life began, but controlling that proclivity in semiconductor manufacturing requires a leap of imagination. Not only must the chemically driven patterns be registered properly for subsequent processing, but the defect level and CDU have to meet industry specifications over full 300mm wafers.

Those requirements have now been fulfilled, according to Chris Bencher and a team from Applied Materials and IBM Almaden Research Center. Their process on full 300mm wafers chemically pinned the PMMA of a PMMA-polystyrene block co-polymer to a lift-off patterned Si-BARC layer to produce ~12nm line/space arrays with 3:1 pitch division. Etching the polystyrene away left 25nm-pitch PMMA lines, 25nm tall, which could then act as a resist layer for pattern transfer into hardmask layers. An optimized process showed no dislocations in the grating pattern and other DSA failure modes were located at the “streets” between lithographic exposure fields where the direction for self-assembly is less clear. The total defectivity was 25/cm2 according to a UVision inspection at 12nm sensitivity – and most defects were particles.

Since DSA requires only some “new bottles of goop,” according to Gregg Wallraff of IBM, it may prove the most economical pitch splitting method. Numerous papers elaborated on the potential for combining 193i with DSA of lamellae to fabricate fine spaced gratings for line-and-cut circuit designs. Others described the fabrication of imprint masters for patterned-media hard disc drives using DSA. The most desired patterns for disc drives are tracks with rectangular domains with a 2:1 aspect ratio, and Elizabeth Dobisz of Hitachi Global Storage explained how such masters could be built with 27nm down-track pitch and 27nm track width. E-beam lithography can directly write the anchoring layer of the lamellar pattern and also cut the lamellae to define tracks at a density of 500Gb/sq.in. Six times that density could be obtained if the read/write heads could adapt to hexagonal arrays of round domains.

EUV Lithography

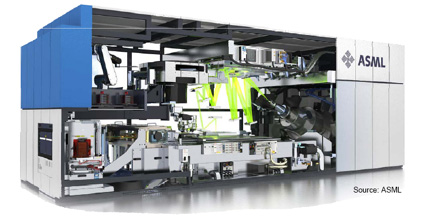

The massive EUV lithography ecosystem slogs on in spite of the skepticism, expressed by Sam Sivakumar of Intel and others, that it may not be ready in time for 10nm node design rule (DR) validation nor for volume production in 2015. Christian Wagner of ASML described the performance of their pilot production tool, the NXE:3100 (figure), two of which have been shipped to customers.

Six lenses have been built with flare <5% reported Wagner. Wafer throughput today is 5wph with 10W sources and, and will rise 10-fold when 105W sources are installed in the first NXE:3300 production tool at the end of the year. Lines and spaces (L/S) have been imaged below 27 nm with 2 nm CDU, and contact hole arrays formed at 60nm pitch and diameters down to 26 nm with conventional illumination. At 32 and 40 nm diameters, the Mask-Error Enhancement Factor (MEEF) is 2 with a 1.8 nm CDU. Using dipole illumination allows for printing of 22 nm L/S arrays with 1.9 nm CDU, 500 nm DOF, and 10% EL.

The machine has been exercised with real 18 nm SRAM metal and contact hole patterns yielding CDU <3nm. Dedicated chuck overlay is <4nm to allow for DP, and stage accuracy is <2nm. Reticles can be handled for 40 cycles before an additional particle is detected, and <3 particles of 40nm-size are dropped on a wafer during a pass. Wager said that Brion Technologies is working on the remaining imaging issues including flare, shadowing, and scattered radiation at chip edges due to reflection by the blades that define the illuminated field at the wafer.

The NXE:3300B EUV stepper for production will be available in late 2012, with a 0.33NA and a flexible EUV illuminator to facilitate improved resolution through source-mask optimization (SMO). With 15mJ/cm2 resist sensitivity and a 250W source, the throughput would be 125wph, according to Wagner.

The first paper about the first NXE:3100 in a fab was by Sungmin Huh of Samsung. He used the EUV scanner to validate different inspection strategies using wafer exposures. The issues all seemed to relate to mask defects, 75% of which came from the substrate and which could not always be detected until they printed on the wafer. Of the 5 mask blank inspection tools tested, only 2 worked at 32nm and one at 16nm. Surprisingly, even wafer inspection did not reveal all the wafer defects! He recommended patterning the EUV absorber in a way that known blank defects are hidden.

Thus in spite of all the progress made on exposure tools, potential insertion of EUVL continues to lag due to delays in ancillary apparatus development, such a mask inspection tools and illumination sources.

EUVL Sources

Two distinct types of EUV sources are being developed by 3 vendors, electrical-Discharge Produced Plasma (DPP) by Xtreme Technologies (now 100% owned by Ushio) and Laser Produced Plasma (LPP) by Cymer and Gigaphoton (50% owned by Ushio). Wagner reports that ASML has integrated four LPP sources that give 80W power at 50% duty factor, and the first DPP source producing 61W at 20% duty factor has also been integrated.

As described by Marc Corthout the Xtreme DPP source uses molten tin transported by two rotating wheels towards the gap between them. A small laser ablates and ionizes a little tin at the gap, which completes a circuit, discharging a 5J capacitor and producing an EUV emitting plasma. Running at up to 40,000 pulses-per-second (pps), the Xtreme system produces 15W of clean EUV at the intermediate focus with +-0.2% dose stability, 0.04% repeatability, 80% uptime, and 1 year lifetime for the collector shells and foil trap. An argon buffer and sputtering keep the condenser optics clean. The first source has been shipped to IMEC. Corthout predicts that higher rep rate energy per pulse will produce 100W by year end, and that the new system designed for the NXE:3300 will produce 350W total. Without the complexity of a drive laser, the DPP system seems quite small.

The Cymer LPP system now produces 11W of clean EUV power at the intermediate focus (IF), averaged over the duty cycle, according to David Brandt of Cymer. It will employ a small laser pre-pulse to prepare a tin droplet for EUV emission with 3% conversion efficiency driven by a much larger laser pulse. He also claimed to meet the 0.2% dose stability spec. and plans to double output by June, all with internal R&D funding. Cymer has produced 10 collector mirrors and has learned how to keep them clean using hydrogen buffer gas. The ASML NXE:3300B tool needs a different and smaller source design, with a 40kW laser and 100kHz drive to produce 250W of EUV at an electricity cost of $350,000/year.

The third EUV source company, Gigaphoton, is targeting October 2011 to demonstrate the GL200E as a 250W source for the NXE:3300B stepper, and is not attempting to support earlier designs. This LPP system uses a short wavelength pre-pulse to vaporize the 20 micron diameter tin droplet before 10.6 micron wavelength driver laser irradiation, achieving 3.3% conversion efficiency with no debris. The force field of a superconducting magnet shields the collector mirror from charged particles, while hydrogen buffer gas controls the rest. In a private interview with BetaSights, Haruku Mizoguchi of Gigaphoton, described a 7 hour experiment in which a 3.6kW CO2 laser pulsing at 100 kHz produced 20W of clean EUV at a 5% duty cycle. Upgrading the laser to 23kW and the conversion efficiency to 5% will produce 250W after spectral filtering, according to Mizoguchi. While the source chamber and magnet are relatively small, the laser system in the sub-fab is absolutely gigantic!

EUVL RET

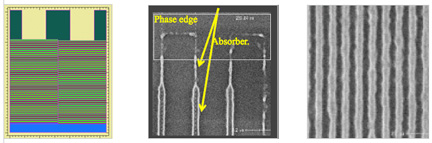

The likelihood that the first production EUV tools will have to operate with k1 factors below 0.5 motivated several papers at SPIE Advanced Lithography. Off-axis and even flexible illumination is now plan-of-record at ASML, and their Brion Technologies division is investigating means of applying EUV proximity correction and even SMO. Perhaps the most remarkable RET paper (7969-119) was by Pei-Yang Yan and a team from Intel and LBL whose poster on fabrication and testing of an EUV alternating Phase-Shift Mask (alt-PSM) was presented orally on Tuesday morning (figure).

EUV alternating Phase-Shift Mask (alt-PSM) work by Intel and LBL, a) mask cross-section, b) absorber and phase-edge resist images, and c) 22nm line-space patterns. (source: Intel)

To achieve a 180° phase shift on a reflective 13.5nm mask at 6° off normal requires a phase step of only 3.39nm. Since that is too small to control, the Intel mask shop fabricated a range of substrate step heights hoping to bracket 420° phase shift at 10.18nm. After multi-layer coating, the phase edges were broadened, but were narrow enough to be largely covered by absorber material. Registering the absorber pattern to the phase steps required depositing a tall frame on the substrate that could be used for subsequent alignment in the second mask pattern generation step, reported Yan.

By shot-gunning offsets, the researchers found properly aligned regions where the images of the absorber and phase steps coincided at the correct effective phase-shift. Resolution was 5 nm better than a binary mask with on axis illumination, the line-end roughness (LER) was superior with particular benefit out of focus, and the alt-PSM dose to size was 30% lower than a binary mask with dipole illumination at the same resolution! The Intel-LBL work did not confront the shadowing predicted for EUV masks by an alt-PSM poster from TSMC, but it did illustrate the heroic measures needed to control the phase in EUVL (to ~0.1nm) given known substrate anomalies.

Optical Lithography Innovations

“Flexibility” was the key word for optical lithography this year, with both Nikon and ASML announcing flexible wavefront tuning and illumination. The second generation ASML FlexRay illuminator has been extensively qualified at IBM, according to Gregory McIntire and a team from the IBM consortium and ASML. The new mirror arrays have overcome the pixel wear-out syndrome plaguing the first generation and mirror assignment algorithms are being developed both to match OPC signatures among tools and to facilitate SMO. Kazuya Fukuhara of Toshiba showed how flexible illumination can avoid mask re-spins when the delivered reticles show defect hot-spots with standard c-quad illumination.

Nikon was much cagier about announcing the capabilities of its Intelligent Illuminator system. According to Tomoyuki Matsuyama of Nikon, it is not sufficient to have a thousand or so tip-able mini-mirrors to properly tailor an illumination pupil. Rather gray-scaling is needed, with 10,000 to 100,000 “degrees of pupilgram freedom” required to properly match the OPC signatures of tools. Such a capability optimizes the process window in SMO, according to Matsuyama, who did not discuss Nikon hardware or when it would be available. Other symposium participants averred that hardware did exist (at least as a prototype) and had been described privately to potential customers.

Nikon was much more forthcoming about its “quick reflex” adaptive mirror which uses actuators on the mirror in the NSR-620D 193i stepper to correct for thermal and other aberrations of the imaging system. According to Jun Ishikawa of Nikon, the mechanical actuators allow near-instant correction of important aberrations using Nikon’s CDU Master analysis system. Dynamic lens control during a scan improves mix-and-match overly and corrects for distortions.

The ASML FlexWave is a plate with local heating and cooling elements that can correct Zernike aberrations Z5 through Z64, which improves the overlapping process window, overlay, and throughput of the XT:1950i, according to Frank Staals. This capability is needed, for example, when widely different illuminations are applied to different layers of a chip printed on the same tool. There is some increase in flare, he admitted, but well within specs. Throughput can be increased to 250wph if corrections do not need to be constantly updated.

Both vendors touted increased throughput of their top-of the line immersion systems and claimed <2nm overlay performance to allow for 32nm production. However, two papers described how single exposure technology could be substituted for double at difficult 32nm and 28nm contact layers. The key trick appears be altering the design to use larger combined geometries where the electrical function and imaging allow, and optimizing the masks for that target. Henning Haffner of Intel suggested that the design community needed a mask optimization tool that would replace an engineer’s intuition for that task.

Design for Manufacturing Doubles Down

The frontier in design process integration is now clearly DP, especially for logic. Since there are two distinctly different DP paradigms (SADP and LELE), designers and software developers are torn. Both have paradoxes and chip failure mode liabilities, according to Yuangsheng Ma of GlobalFoundries. Some design features may have to be abandoned; routers and placement tools will need to be aware of DP prohibitions. With care and the use of the block layer to define SADP features, the methods explored for memory can be adapted to logic, reported Ma.

Lars Liebmann of IBM was not so sanguine. He warned that industry-wide standards need to be developed for DP or it will “fail” the way alt-PSM “failed.” Only this time, there may not be an economical alternative for continuing Moore’s Law in most of the industry. Liebmann explained that 80nm was really the final pitch limit for single exposure with water immersion technology and it will be reached at the 22nm node in 2012. Then what? Restrictive resign rules (RDR)? Decomposition-aware design rule checking (DRC)? The industry must decide, and then develop tools that can report actionable errors to designers as well as transmit the “color information”-the multiple patterns needed for a single mask layer-downstream from standard cell libraries to placement tools and routers in the EDA flow.

Liebmann advocated a strategy of “anchored coloring plus smart placement” to avoid conflicts while minimizing area increase. The coloring on one level requiring double patterning affects the layout on the next, which then affects the coloring and so on. Liebmann predicted that the 20nm node would require 3 levels of DP, and that 14nm would require 7 levels of DP with at least one triple-patterned layer thrown in! We really must hope that EUV or EbDR will work efficiently soon enough, so that designers do not have to chase coloring conflicts through 7-8 layers to build chips selling for a few dollars for a few months in not many years from now! – M.D.L.

Tags: 10nm, 16nm, 193i, 20nm, 22nm, a-Si, Advanced Lithography, ALD, alt-PSM, ArF, ASML, CAR, CDU, Cymer, DFM, Dow, DP, DPP, DR, DSA, EbDW, EDA, EUV, EUVL, GDR, Gigaphoton, IBM, IC, IMEC, Intel, LELE, LER, Levenson, litho, logic, LPP, LWR, materials, MEEF, Nikon, OPC, PAG, RDR, RET, RSADP, SADP, Samsung, SPIE, SRAM, TEL, TSMC, Xtreme