Friday, January 30th, 2009

Ziptronix wants to help you with your 3D roadmap. The IP spin-out from Research Triangle Park, NC is now actively negotiating licenses to its unique wafer-to-wafer (W2W) and die-to-wafer (D2W) bonding technologies. Using treated-oxide (with surface treatments) and nickel (with a mystery metal) as the connecting materials, room temperature bonding with up to 108/cm2 of 3D interconnects could soon begin with little additional process equipment capital expenditures at IDMs, foundries, and OSATs.

According to Ziptronix CEO Dan Donabedian, the company has worked for nearly a decade to be able to deliver the low temperature IC bonding process that is needed to make true 3D IC integration a practical reality today. “We’re currently engaged in substantive licensing discussions with customers in multiple market segments at all levels in the semiconductor supply chain, and we anticipate that several license agreements will be reached in the coming months.”

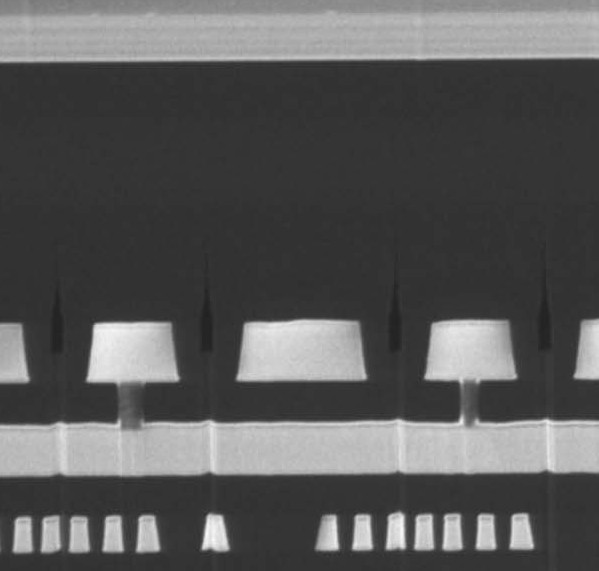

As Phil Garrou summarized last year, Ziptronix low-temperature oxide bonding technology allows for nickel interconnects to copper, tungsten or aluminum TSVs. Donabedian stated, “Because of the depth and breadth of our patent portfolio, we believe that virtually any use of low temperature oxide bonding processes is likely to be covered by one or more of our patents.” The company has already shown the ability to bond InP chips to Si (see Figure).

According to a recent study by Yolé Development, the Ziptronix DBI process was the lowest cost bonding technique when compared to Cu-Cu (copper-to-copper thermal compression) and adhesive technology. In this study, the bonding costs per wafer level (including CMP) were: $57 for Cu-Cu; $22 for adhesive; and just $12 for the DBI technology. The cost savings are due to fast bonding (~2 min. vs. 30-60 min. for Cu-Cu) and no compression being needed so that standard pick-and-place tools can be used. –E.K.

Tags: 3D, bonding, IC, InP, integration, IP, Ni, oxide, Si, TSV