Tuesday, August 4th, 2009

While EUV Lithography may now be inevitable, according to SEMATECH Program Manager Bryan Rice, it may not be indispensable. SEMICON West offered a snapshot of progress towards the 32nm, 22nm, and 16nm device nodes at the Device Scaling TechXPOT, and the industry appears to have patterning options even if EUV encounters further delay.

Yan Borodovsky of Intel spoke about lithography options for high volume manufacturing. For Intel, pitch splitting – PS, a generalization of double patterning – with 193nm illumination is the default option through the 16nm node. Of course, for Intel, 16nm devices are fabricated at 60nm pitch, 30% larger than industry convention. Even so, implementing high volume manufacturing at 16nm in 2013 can be done with 193nm immersion exposure tools and an infrastructure that exists today. It just will take more exposures and processing.

Yan Borodovsky of Intel spoke about lithography options for high volume manufacturing. For Intel, pitch splitting – PS, a generalization of double patterning – with 193nm illumination is the default option through the 16nm node. Of course, for Intel, 16nm devices are fabricated at 60nm pitch, 30% larger than industry convention. Even so, implementing high volume manufacturing at 16nm in 2013 can be done with 193nm immersion exposure tools and an infrastructure that exists today. It just will take more exposures and processing.

Beyond 16nm, the options were more difficult and uncertain. Borodovsky reported that Intel hoped to implement 11nm at 40nm pitch with pitch splitting in 2015, even though the ITRS did not call for 40nm pitch until 2017. If there were a next generation lithography tool  demonstrated at that resolution then Intel would consider it, but the window for 11nm high volume manufacturing closes in 2011, Borodovsky warned. He suggested that there were 3 possible follow-on technologies: EUV, Imprint, and direct-write e-beam. None seemed likely for main-stream production, although he allowed that some new lithography technology could usefully compliment pitch splitting on low density layouts.

demonstrated at that resolution then Intel would consider it, but the window for 11nm high volume manufacturing closes in 2011, Borodovsky warned. He suggested that there were 3 possible follow-on technologies: EUV, Imprint, and direct-write e-beam. None seemed likely for main-stream production, although he allowed that some new lithography technology could usefully compliment pitch splitting on low density layouts.

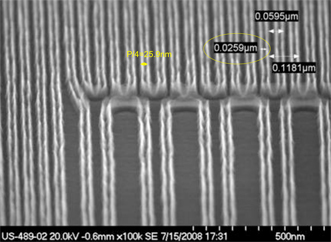

Borodovsky also showed a pitch quartering (P/4) approach to 7nm lines (28nm pitch) fabricated with one 193 immersion mask exposure and two steps of sidewall-spacer pitch-splitting. Thus the initial pitch was 112nm, well within current technology. Cutting such patterns into useful circuit element certainly requires more exposures and processing, but that, by definition, occurs at lower density.

Imprint

Mark Melliar-Smith, president of Molecular Imprints, Inc., predicted continued expansion of the market for imprint lithography in an exclusive BetaSights interview at SEMICON West. He sees MII’s core market as data storage, both hard disk drives and non-volatile semiconductor memory. Both have challenging resolution and cost requirements coupled with more tolerance of defects than logic/MPU lithography. Imprint has intrinsically low cost due to the simplicity of the tool and low consumption of resist, he said.

Mark Melliar-Smith, president of Molecular Imprints, Inc., predicted continued expansion of the market for imprint lithography in an exclusive BetaSights interview at SEMICON West. He sees MII’s core market as data storage, both hard disk drives and non-volatile semiconductor memory. Both have challenging resolution and cost requirements coupled with more tolerance of defects than logic/MPU lithography. Imprint has intrinsically low cost due to the simplicity of the tool and low consumption of resist, he said.

The mask issue is being addressed through a partnership between MII and DNP, the leading mask house. DNP can already make 2x generation master masks, repaired to have zero defects, but their cost is >$150,000. Soon, they will implement an imprint replica process to make much less expensive working masks for printing on wafers. With MII’s help, DNP hopes to make hundreds of replicas per master, and each replica would then print hundreds of wafers. MII’s first generation high volume single head manufacturing tool for semiconductors is scheduled for delivery in 2011, with 8nm overlay and 20 wph throughput. A cluster tool would follow in 2013.

In the hard disk drive business, MII has 11 orders with 9 tools shipped. High volume manufacturing (at 350 two-sided-disks/hour) will begin this year on the first cluster tool, at a resolution below 20nm. The disk makers themselves had taken on the task of making the replica templates for production, rather than relying on the mask industry, according to Melliar-Smith. Headcount at MII has grown to 127 and hiring continues as tool production ramps up for the magnetic and semiconductor data storage markets.

EUV Hunger

Borodovsky and others are still betting that EUV will be the follow-on technology to pitch division with 193nm water immersion exposure, but when it will happen and at what cost remains uncertain. Bryan Rice of SEMATECH reported that there still remained 3 major roadblocks: the source, line width roughness in the resists, and defectivity still 100x acceptable. While optical tools can inspect 40nm EUV masks, SEMATECH has undertaken to build 3 prototype actinic inspection prototypes. According to Rice, actinic inspection tools need to be produced commercially – and soon.

Borodovsky and others are still betting that EUV will be the follow-on technology to pitch division with 193nm water immersion exposure, but when it will happen and at what cost remains uncertain. Bryan Rice of SEMATECH reported that there still remained 3 major roadblocks: the source, line width roughness in the resists, and defectivity still 100x acceptable. While optical tools can inspect 40nm EUV masks, SEMATECH has undertaken to build 3 prototype actinic inspection prototypes. According to Rice, actinic inspection tools need to be produced commercially – and soon.

Bruno La Fontaine of Global Foundries pointed out that, while EUV wasn’t ready for high volume production, its competitors weren’t either. Thus, there were no technologies to exercise. He claimed that EUV would be cost comparable with pitch splitting for wafer runs of 5000 if the exposure tool could run at 60wph and cost the same as the DUV scanner – so long as the mask cost was in the same ball-park as DUV. He noted that only 10% of the defects found on EUV masks printed – probably a result of the higher image quality. When would EUV be ready for pilot production? La Fontaine speculated that 2014 was possible, but not certain. By then Borodwski and Intel expected to be splitting their way to 11nm, requiring NA>0.25 and RET for the EUV tools to be competitive.—M.D.L.

Bruno La Fontaine of Global Foundries pointed out that, while EUV wasn’t ready for high volume production, its competitors weren’t either. Thus, there were no technologies to exercise. He claimed that EUV would be cost comparable with pitch splitting for wafer runs of 5000 if the exposure tool could run at 60wph and cost the same as the DUV scanner – so long as the mask cost was in the same ball-park as DUV. He noted that only 10% of the defects found on EUV masks printed – probably a result of the higher image quality. When would EUV be ready for pilot production? La Fontaine speculated that 2014 was possible, but not certain. By then Borodwski and Intel expected to be splitting their way to 11nm, requiring NA>0.25 and RET for the EUV tools to be competitive.—M.D.L.

Tags: 11nm, 16nm, 193i, 22nm, 7nm, EbDW, EUV, IC, ITRS, litho, NIL