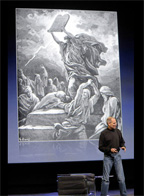

… and after years of tribulation with most people gone to other lands, a great fear was upon the land of Publishing for all business models were lost along with all hope. The web had washed so much away, and the multitudes prayed that the one true Jobs would intervene and with compassion bestow upon the world a great new Device and Transaction Services Thereof. And having agreed to foresake all other OSs, the prayers of the multitudes were answered today when Jobs revealed the iPad. And they saw that it was good.

This is the 100th BetaBlog post, and today is the day that Apple released the iPad. Consequently (unlike most posts about high-tech manufacturing; try clicking in the Tags-cloud, Categories, or Archives), this is about the business of publishing and the dynamics thereof. Ancient Greek theatrical stagings often involved a person playing the role of a god (Lat. “Deus”), who would appear from (Lat. “ex”) the top of the stage being lowered by a machine (Lat. “machina”) to resolve difficult plot twists; consequently, “deus ex machina” has come to mean something like devine intervention. The commercial publishing industry—long suffering from a broken business model with no hope for the future—has been praying for just such a “Jobs ex machina” intervention.

This is the 100th BetaBlog post, and today is the day that Apple released the iPad. Consequently (unlike most posts about high-tech manufacturing; try clicking in the Tags-cloud, Categories, or Archives), this is about the business of publishing and the dynamics thereof. Ancient Greek theatrical stagings often involved a person playing the role of a god (Lat. “Deus”), who would appear from (Lat. “ex”) the top of the stage being lowered by a machine (Lat. “machina”) to resolve difficult plot twists; consequently, “deus ex machina” has come to mean something like devine intervention. The commercial publishing industry—long suffering from a broken business model with no hope for the future—has been praying for just such a “Jobs ex machina” intervention.

Ever since Stewart Brand said something that included the phrase “information wants to be free” in 1984, without particularly contemplating the ramifications, most people have thought that for some reason information should be exchanged without a transfer cost. The architects/designers who developed internet software over the last 25 years did so with the idea that information will flow without transfer costs, and that any money involved would be made by ISPs and access device makers.

Starting with digital audio recordings of popular songs, Apple created the iTunes internet store. In so doing, iTunes established a vital new business model and distribution method during a period when nothing else worked. At this point it is not absurd to say that Apple led by Jobs saved the music industry.

The most recent attempt by the publishing industry—specifically Time, Condé Nast, Meredith, the News Corporation and Hearst—to save itself was the recent creation of the Next Issue Media consortium that plans to run its own online store selling digital issues and collecting consumer information. “It’s fundamental to the business model of publishers. We’ve always enjoyed an opportunity to know exactly where our consumers are, and be able to market other products to them,” said John Squires, the interim managing director of the consortium. “It’s a very key issue for the founding members of this business.” The consortium includes only some of the world’s major publishers, and they have not yet disclosed details of their “open” standards, so this direction is still uncertain.

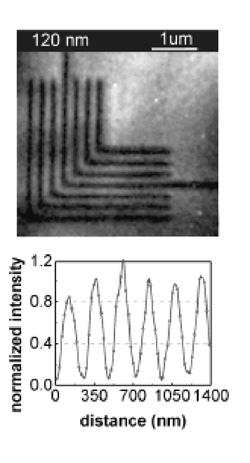

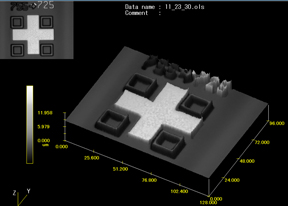

Meanwhile, Apple’s new iPad will use the EPUB electronic publication format, which is also supported by Adobe’s Digital Editions software. With all EPUB files to be distributed through an Apple website, just as people are willing to pay a few dollars for audio and video files, people may soon get used to paying modest amounts for electronic books, magazines, newsletters and dailies (figure). Publishers will lose control of their audience to Apple, but Apple will provide a paying and growing audience.

Though we knew that a subscription business model was a risk, BetaSights was originally founded one year ago to sell niche specialized newsletters. However, due to the conceptual momentum of the recent past, most people were not willing to pay for a newsletter and so we stopped its publication. This blog page remains as an example of our topical expertise and writing style, while we have spent more time on consulting projects for clients.

Now that the iPad and transaction services thereof have been revealed to the world, we all have a few months to get used to the possibility of a major change in our information world. Perhaps a day will come when everyone will see that information is valuable (not free), and that value varies with quality. After a while, we’ll probably all get used to subscribing to a few quality niche e-newletters. At that time, maybe the BetaSights Newsletter will re-exist as one of your favorities…—E.K.