Friday, March 13th, 2009

Trust is the foundation of all trade and business. Without trust, no deal can get done, no venture can be launched, no discussion can even begin. Trust has been shaken in individual businesses in recent years, but recently exposed financial scams have shaken confidence not just in one or a collection of companies but almost in the very value of money itself. Agencies gave high ratings to the long-term stability and value of CDO (collateralized debt obligations), which in the sober light of day are seen to have been illusions disguised by algorithms. If we can’t trust banks then maybe we can’t trust fabs?

Trust is the foundation of all trade and business. Without trust, no deal can get done, no venture can be launched, no discussion can even begin. Trust has been shaken in individual businesses in recent years, but recently exposed financial scams have shaken confidence not just in one or a collection of companies but almost in the very value of money itself. Agencies gave high ratings to the long-term stability and value of CDO (collateralized debt obligations), which in the sober light of day are seen to have been illusions disguised by algorithms. If we can’t trust banks then maybe we can’t trust fabs?

Intel claims to have invested billions of dollars into R&D for exotic new materials for it’s chips, including what can be incomprehensible acryonyms like HKMG and SiGe and CDO. How can we trust another CDO? Well, this CDO is “carbon-doped oxide” which is completely trustworthy because it’s been used for over a decade in mainstream chips (CDO at Intel is called “SiCOH” at IBM and “Black Diamond” by Applied Materials and “Aurora” by ASM and “Coral” by Novellus; it’s all essentially the same functional thin-film glass used to insulate the metal wires on chips). The world’s fab technology really works. I use it to write these words, and you use it to read these words.

Fab technology, whether semiconductor, flat-panel, photovoltaic, or MEMS, is about making incredibly useful things for amazingly low costs. The world needs these things. Another billion people need a cell phone, and it still needs a lot of chips. Microcontrollers and sensors and renewable energy all enrich people’s lives across the world in myriad ways, and demand will not stop. However, we are part of the global economy now, and so we too must slow when everyone else slows.

The trust has never left fabs. Fab folks want to do things, we like to make things happen, it’s just what we do. When the global economy turns around, we’ll be ready to ship products. We still know who to call at midnight to get a needed part. We still trust our order will show up on time and to spec. Our CDO is in no way similar to their CDO, trust hundreds of dedicated technologists who gather every year for the International Interconnect Technology Conference (June 1-3, in Sapporo for the first time). A reminder as to why TSMC is not an accurate bellwether during a downturn will be covered in the Newsletter. –E.K.

Tags: CDO, fab, FPD, IC, MEMS, PV, R&D

Posted in fab, FPD, IC, MEMS, PV | Comments Off on Trust your fab – CDO vs CDO

Thursday, March 12th, 2009

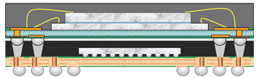

Stangl Semiconductor Equipment has launched its Linea horizontal inline wet process platform for cleaning and etching of crystalline silicon PV wafers. The fully-automated dry-in/dry-out system offers reliable production capacity of up to 3,400 wafers per hour (wph) corresponding to an estimated 60 MW per line running 156mm wafers. The system can also be configured at 1,700 wph and then doubled. The tool was first shown at Photon’s 4th Photovoltaic Technology Show 2009 Europe in Munich.

To reach such high throughput levels, essential for low-cost solar cell manufacturing, handling of wafers as thin as 150 microns must be managed carefully. The tool is based on two newly developed sub-systems for transport and chemical flow, though no information on beta tests was available at the time of this posting.

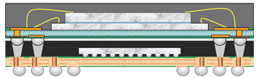

Linea inline wet processing (source: Stangl)

The continuous inline process transport (see figure) and the overall wafer handling are designed to ensure a low breakage rate. When wafers eventually break, and at high volume the odds say it’s only a matter of time, the handling systems must be cleanable and unbreakable. The wafer transport sub-system uses a motor-driven plastic conveyor chain to smoothly move O-ring-based belt transfer sections. Gentle motion of 156 mm or 125 mm wafers minimizes mechanical wafer stress across up to 6 parallel transport lanes.

The chemical flow sub-system reaches both high uniformity and reduced chemical consumption. Spray nozzles deliver chemicals to wafer top sides, and careful control of chemical flows, rinse water flows, and dry gas flows allow for effective isolation between inline process sections. Well designed continuous processing tools are the way to go to get to cost-effective high volume. –E.K.

Tags: chemical, clean, etch, inline, PV, Si, wet

Posted in Equipment, fab, Product, PV | Comments Off on Stangl inline PV wet tool

Wednesday, March 11th, 2009

Nanometrics today announced the release of Version 2.0 of its NanoCD Suite of solutions for optical critical dimension (OCD) metrology, just one year after V1 was released. OCD (a.k.a., “scatterometry”) has been used to successfully control fab processes for many years. The major known limitation of the technique is model building from reference metrology data, so Nanometrics has upgraded the software development tools to accelerate model building.

NanoCD Suite (NanoGen, NanoMatch, NanoStation and NanoDiffract) for OCD metrology (source: Nanometrics)

The new OCD suite is made up of components which allow for scalable fab-wide metrology solutions: NanoDiffract, NanoGen, NanoMatch, and NanoStation (see figure). The NanoDiffract is the software that runs in various hardware boxes. NanoGen is an offline server-based library generation system that can support numerous users and systems, while NanoStation is an offline desktop system used for recipe and library generation. NanoMatch is a computer providing real-time analysis that runs within another metrology system: standalone Atlas XP and Atlas-M for wafers and reticles, and the IMPULSE/9010 integrated metrology family.

“Many customers are applying our NanoCD technology for measurements in every sector of the fab, including thin film, CMP, advanced lithography and etch applications on complex 32nm and 22nm node test structures,” commented Nagesh Avadhany, vice president of Applications at Nanometrics. As was reported from SPIE 2008 by this editor, OCD measurement precision of <1% has also been shown for finFET gate stack characterization; measuring in the fin area seems to provide sufficient resolution for process control for both the high-k and metal-gate depositions.

Enhancements in NanoDiffract allow users to control their process based on measurements of key parameters directly on DRAM, Flash, and SRAM cells. This measurement capability allows process engineers to optimize their metrology recipe and determine sensitivity even before initial wafers are processed. This highly optimized workflow for OCD applications development results in much faster time to results leading to claims of rapid production deployment, higher productivity, and lower cost of ownership. –E.K.

Tags: 22nm, 32nm, CD, CMP, etch, fab, finFET, high-k, HK, IC, metal-gate, metrology, MG, OCD

Posted in Equipment, fab, IC, Product | Comments Off on Nanometrics next NanoCD Suite for OCD

Tuesday, March 10th, 2009

Bob Metcalfe is very smart, very successful, and very rich. Now an unashamed venture capitalist investing in both PV and home nuclear as part of his diversified portfolio, his major vision is for a new “enernet” that would fundamentally revolutionize the energy industry. He spoke of this as well as his invention of Ethernet this evening at the Computer History Museum in Mountain View, California. “Just as it took 30 years to break the communications monopoly, with energy it will probably take 30 years to break the energy monopoly and be able to create new affordable energy sources for the world,” postulated Metcalfe.

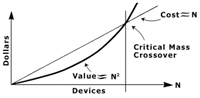

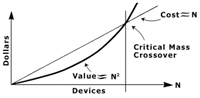

Trying to sell the value of networked PCs back in the 1980s, he decided that the value increased approximately as the square of the number of connections, which is what gave us “Metcalfe’s Law” (see figure). So the major commonality between Metcalfe’s and Moore’s Laws is that each one was originally just a marketing tool (the term used by Moore at a previous Computer History Museum event).

Trying to sell the value of networked PCs back in the 1980s, he decided that the value increased approximately as the square of the number of connections, which is what gave us “Metcalfe’s Law” (see figure). So the major commonality between Metcalfe’s and Moore’s Laws is that each one was originally just a marketing tool (the term used by Moore at a previous Computer History Museum event).

“Metcalfe Law has never been numerically evaluated. What is value, what is connected, what is a user?” quipped Metcalfe. In all seriousness, he talked about reasonable attempts to quantify his namesake law. “If you do the math, the critical mass depends on the cost of the connection and the value of the connection,” explained Metcalfe about the current effects of the internet and new devices. “The critical mass is heading down.”

The energy grid today has limited capacity, is very synchronous and fragile, and so it reminds Metcalfe of the computer world of the 1980s. “We need some research on what the smart grid of the future will look like,” he said. From first principles, it needs a control pane, standards, storage, and it should be far more symmetrical (in terms of allowing for safe metered energy to flow both in and out), etc. “Maybe the internet will be the control pane,” continued Metcalfe. “Maybe we should give up on AC and go back to DC as Edison wanted.” More on Metcalfe and innovation will be in the BetaSights Newsletter. –E.K.

Tags: net, PV

Posted in IC, PV | Comments Off on Metcalfe envisions energy net

Monday, March 9th, 2009

SVTC Technologies has been busy announcing new business directions ever since Joe Bronson stepped in as CEO at the beginning of this year. Last month it announced a partnership with Entrepix to provide 300 mm chemical mechanical polishing (CMP) development and production services for customers who use the Tool Access Program (TAP) at the SVTC fab in Austin, Texas. Today it announced an expansion of its Analytical Services capabilities to encompass markets beyond its traditional base of silicon chip-based industries; SVTC Analytical Services will tout its expertise at Pittcon 2009, being held March 8 to 13 in Chicago.

SEM bay (source: SVTC Technologies)

“Our approach can be of enormous benefit for essentially any industry that must analyze or inspect elements, molecules and other tiny structures – including aerospace and defense, electronic materials, emerging energy technologies, fabless semiconductor development, IC manufacturing, life sciences and biotechnology, metal and alloy manufacturing, and semiconductor equipment,” said Julian Searle, Business Development Manager of Analytical Services for SVTC.

The company has a full suite of advanced analysis tools and people with the experience to coax useful signals out of SEM (see figure), TEM, STEM, SIM, FIB, ICP-MS, and other precise acronyms. “What’s unique is the way we apply a commercial management approach to areas that have traditionally been the domain of research laboratory systems,” said Jack Blaha, General Manager of Technology Services for SVTC. “It’s this combination of strong research skills with the rigor and discipline of a commercial approach that enables us to not only look for new ways to do things that haven’t been done before, but then to also make these innovative processes repeatable, accurate and sustainable for our customers.”

“SVTC’s Analytical Services has consistently proven to be a valuable resource for process and yield analysis for Nantero,” said Greg Schmergel, CEO and co-founder of Nantero, a nanotechnology company using carbon nanotubes for the development of next-generation semiconductor devices. “The combination of state-of-the-art tooling and very experienced personnel ensures that results are clear and correct the first time. Our company performs work at multiple sites, and due to the high-quality services and fast turnaround time from SVTC, we have been routing more of our analytical work to SVTC due to the value they add toward achieving our objectives.” -E.K.

Tags: AFM, analysis, EELS, FIB, IC, materials, MEMS, SEM, SIMS, TEM

Posted in fab, FPD, IC, MEMS, Product, PV, Service | Comments Off on SVTC provides analytical services

Friday, March 6th, 2009

Veeco announced yesterday that it has entered into a strategic partnership with Daiyang Metal of Korea, a leader in the production of cold rolled stainless steel, to be its supplier of equipment to manufacture CIGS solar cells. As a first milestone in this relationship, Daiyang has placed an initial multi-million dollar purchase order with Veeco for its complement of FastFlex Web Coating Systems to build a thin-film CIGS solar cell production line in Yesan, Korea. Veeco currently expects to ship these systems during the fourth quarter of 2009, after which it expects to firm up a follow-on order with Daiyang.

Rotary cathodes inside FastFlex (R2R) deposition system (source: Veeco)

This complement of tools is comprised of one Mo (Molybdenum) deposition system, one TCO (Transparent Conductive Oxide) deposition system and two CIGS deposition systems. Veeco’s FastFlex platform features flexible architecture with high uptime that can be configured to specific needs, with a choice of planar or rotary magnetrons (see figure) for high throughput, high temperature effusion sources, and substrate sizes up to one meter wide.

Chan Ku Kang, CEO of Daiyang, commented, “Daiyang Metal has an aggressive multi-year, multi-site plan to become a leading worldwide manufacturer of CIGS solar cells. Our short term goal is to aggressively ramp to 200MW capacity during 2010 and 2011, which will entail the purchase of additional Veeco systems. Ultimately it is our goal to achieve one gigawatt of CIGS production capacity by 2013. We spent a lot of time researching and surveying the suppliers of CIGS manufacturing tools, and were very impressed with the level of process support and collaboration we received from Veeco during that period. We chose Veeco because they are best prepared to meet our manufacturing and technology needs today and in the future.”

Market research firm Nanomarkets estimates CIGS production capacity will reach 1.4 GW in 2012 and 4.9 GW in 2015 (a 30x increase over 2008’s 152 MW). Companies such as NanoSolar, HelioVolt, and Solyndra each pursue unique CIGS deposition technologies to control the proper film properties. Piero Sferlazzo, senior vice president of Veeco’s Solar Equipment business, commented, “Thermal source technology is quickly becoming the preferred CIGS deposition method because it provides customers with high volume, low cost manufacturing solutions that drive down the manufacturing cost per watt.” Previous thermal evaporation tools reportedly lacked the control needed to ensure proper CIGS stoichiometry for high PV cell efficiency. –E.K.

Tags: CIGS, Mo, PV, R2R, solar, TCO, thin-film

Posted in Equipment, fab, Product, PV | Comments Off on Veeco and Daiyang partner for R2R CIGS PV

Thursday, March 5th, 2009

Amkor Technology announced today that it will introduce its next generation package on package (PoP) platform at the IMAPS Device Packaging Conference next week in Scottsdale, AZ. Again begging the question, “Who needs TSV?” this this new PoP platform uses Amkor’s proprietary through mold via (TMV)(TM) interconnect technology to get to 3D IC stacking. {Blog update, Amkor’s Lee Smith provided the correction that TMV is package-level technology that is indepedent of TSV, see BetaBlog 090316.}

As first shown last year at ECTC, TMV allows scaling of the PoP stacked interface to 0.4mm pitch along with larger silicon area within an existing package footprint in support of emerging high density memory architectures. Expanding on the company’s BGA and CSP technologies, this new package supports flip chip, wirebond, stacked die and passive integration within the bottom package for increased integration and design flexibility. Package warpage is also reportedly reduced. Nominal final package thickness is 1.24 mm, based on a 250 µm thick TMV layer and a 400 µm thick cap over the wire-bond stack (see figure).

Through mold via (TMV) package-on-package (PoP) technology using wire bonds, TSV option not shown (source: Amkor Technology)

“Amkor has been investing in the building blocks of our TMV approach for a number of years and we are pleased to bring this powerful new technology to market,” commented Tim Olson, senior vice president of R&D and emerging technologies for Amkor. “We have successfully passed our internal qualification and are making preparations to support our ramp into production. We have also initiated the JEDEC registration process to facilitate industry standardization.”

The company has not publicly disclosed the TMV process flow, but the sloped via sidewalls are key to allowing the use of solder balls as the conductor fill. Using 0.4mm pitch 2-row stacked interfaces with a 10mm flip chip, TMV allow for 961 bottom balls and 232 interconnect balls within a 13mm package body size. The company says that this stacked interface will scale with solder ball pitch densities to 0.3mm or below. –E.K.

Tags: 3D, IC, memory, PoP, TMV, TSV, WLP

Posted in fab, IC, Product, Service | Comments Off on Amkor’s TMV PoP will go to 0.3mm

Wednesday, March 4th, 2009

Electron beam direct write (EBDW) lithography is well-developed and has better potential resolution than any other method, but writing speeds did not keep up with Moore’s law after about 1980, leading to abysmal throughput (measured in hours per wafer). Now, the e-Beam Initiative focusing on design for e-beam manufacturing (DFEB) and multibeam writing using MEMS technology promise to make it practical, at least for prototyping and short production runs.

A group of 20 leading companies announced the launch of the eBeam Initiative, a forum dedicated to explaining and promoting design for e-beam (DFEB) on February 24. D2S serves as the managing sponsor of Initiative. The formal steering group for the eBeam Initiative consists of Advantest, CEA/Leti, D2S, e-Shuttle, Fujitsu Microelectronics, and Vistec. Practical e-beam manufacturing would also reduce the need for round-A fabless companies to invest in mask sets. One goal of the eBeam initiative would be to establish e-Beam foundries serving those markets. At present, there are very few.

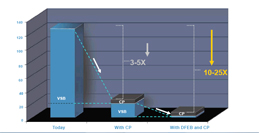

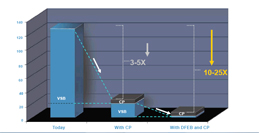

The enabling technology for the eBeam initiative is character projection (CP), where the electron beam is shaped by a stencil near the source and then demagnified, forming an image on the wafer (Ref: BetaBlog 090126). Using CP instead of a variable-shaped beam (VSB) improves writing time by 3-5X. If the designs are optimized for character projection, the throughput improvement becomes 10-25X (see figure), and such designs could print at 1 wph, according to Fujimura.

The enabling technology for the eBeam initiative is character projection (CP), where the electron beam is shaped by a stencil near the source and then demagnified, forming an image on the wafer (Ref: BetaBlog 090126). Using CP instead of a variable-shaped beam (VSB) improves writing time by 3-5X. If the designs are optimized for character projection, the throughput improvement becomes 10-25X (see figure), and such designs could print at 1 wph, according to Fujimura.

The throughput problem in EBDW results directly from Coulomb’s law: put enough electrons into a high resolution “pencil” beam to expose resist quickly and their electric fields will push them apart, ruining everything. Of the solutions that use a great many low current beams in parallel, Mapper Lithography from Holland is, perhaps, the furthest along. The 50kV PML2 system from IMS Nanofabrication AG of Austria has 43,000 beams working in an alpha-tool. With DARPA support, KLA-Tencor has entered its Reflective e-beam lithography (REBL) Nanowriter in the world-wide competition. Details about these technologies, and additional perspectives regarding the eBeam Initiative will be in the next issue of the BetaSights Newsletter. –M.D.L.

Tags: 22nm, 32nm, 45nm, e-beam, EbDW, IC, litho, node

Posted in Equipment, fab, IC, MEMS, Product | Comments Off on eBeam Initiative and tool competition

Tuesday, March 3rd, 2009

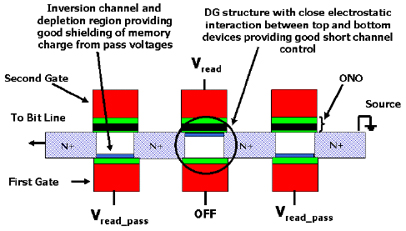

IEDM 2008 included the unveiling of Schiltron’s (Session 34.6) revolutionary 3-D high density Flash technology that combines the smallest TFTs to date in series strings of up to 64 cells. The unique architecture effectively removes pass disturbs allowing large worst-case string currents and resulting in thinner tunnel oxides, lower erase voltages, and higher endurance than the existing nitride-based NAND approach. Feasibility of the approach was shown using existing CMOS fab tooling without new materials being needed.

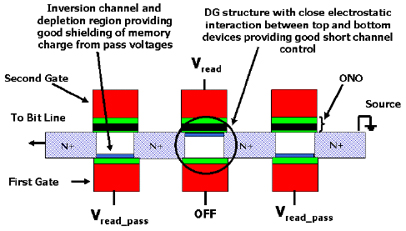

Cross-sectional schematic of the proposed dual-gate thin-film-transistor semiconductor-oxide-nitride-oxide-semiconductor (DG-TFT-SONOS) type Flash structure (source: Schiltron Corp.)

Unique properties of antimony in silicon allow multilayer monolithic 3-D stacking. The “Schiltron Solution” uses a double-gate (DG) which provides close electrostatic interactions to control short channel effects. The DG structure is certainly scalable (see figure), reportedly has zero pass disturbs, and is easily stackable due to “freezing” of the source/drain dopants. With 48nm Lg and 35nm channel thickness in the burried gate, a loose definition could term this a “nanowire” device, which would suddenly make chips based on this structure the nanowire memories that are the closest to production reality.

To erase the cell, you invert the back gate and apply the erase voltage to the top gate. Since only electrons, not hot holes, are needed to erase this device it lends itself to cycling endurance. You can use the thin tunnel oxide without damage; 32 cell strings tested under accelerated lifetime conditions showed that the devices should withstand 10 years at 85°C with good results.

Only industry standard CMOS processes and materials are used to fab this device, allowing Schiltron the flexibility of developing the integrated process flow with any advanced digital CMOS foundry. “We’re riding on the coat-tails of CMOS and the standard tooling,” explained Schiltron founder and president Andrew Walker. More details in this week’s BetaSights Newsletter. –E.K.

Tags: 3D, 45nm, CMOS, Flash, IC, memory, NAND, SONOS, TFT

Posted in fab, IC | Comments Off on IEDM2008 DG-TFT SONOS shown

Monday, March 2nd, 2009

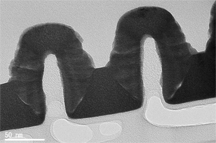

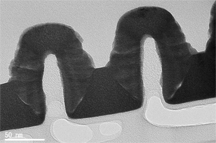

Partners SII NanoTechnology and Carl Zeiss NTS have joined with ASML R&D and Toshiba’s process and manufacturing engineering groups to show a new way to create accurate cross-sections of soft photoresist and low-k dielectric lines in dense circuit patterns. First shown in a poster paper at SPIE last week was the ability to generate accurate 2D profiles for <45nm resist lines, using argon-beam induced deposition (ArBID) of a thin tungsten (W) coating (see figure).

ArBID of W coated 45nm node resist lines (source: SII NanoTechnology)

Physical cross-sections of structures are required to calibrate other metrology tools (whether CD-SEM or scatterometry), and it is inherently challening to cut a soft material without smearing the edges. Even at the nanoscale where the cut is done with a focused ion beam (FIB) inside of a scanning electron microscope (SEM) chamber, when every nm counts it is difficult to not distort shapes. A thin coating of metal over the surface has traditionally been used to preserve soft strucutres, and until the 45nm node the process of record was platinum (Pt) deposited in the e-beam column of the SEM. However, 15-20% shrinkage in 45nm node resist line heights has been seen due to the e-beam coating, so a more gentle metal deposition was needed.

A TripleBeam metrology system consists of SEM, FIB, and Argon columns. The SEM column is mainly used for imaging, the FIB column is used for material removal, deposition, and imaging (e.g. grain boundaries in metals), while the Ar column cleans and does small amounts of removal and deposition. The Argon column has a relatively large spot size compared to a FIB, and so the local species flux is relatively small. Using a static Ar beam at 600V and 2.5 nA to minimize the local dose rate for tungsten (W) deposition, scanning transmission electron microscope (STEM) images of 45 nm dense lines (photoresist on BARC) have been made.

Using the FIB in the triple beam system, Toshiba was able to generate TEM images of 55nm dense contact holes. The measured resist height with STEM and scatterometry matches within 3% using ArBID, and can be applied for the calibration of scatterometry models used to control CD after litho and before etch in the fab. 3D metrology using STEM is feasible with good total measurement uncertainty (TMU) after averaging together the data from 50 profiles. Further research is needed to find out if ArBID can be applied for the 32nm node. –E.K.

Tags: 32nm, 45nm, APC, Ar, calibration, FIB, linewidth, metrology, SEM, TEM

Posted in Equipment, fab, IC, Product | Comments Off on ArBID allows nanoscale cross-sections

Trust is the foundation of all trade and business. Without trust, no deal can get done, no venture can be launched, no discussion can even begin. Trust has been shaken in individual businesses in recent years, but recently exposed financial scams have shaken confidence not just in one or a collection of companies but almost in the very value of money itself. Agencies gave high ratings to the long-term stability and value of CDO (collateralized debt obligations), which in the sober light of day are seen to have been illusions disguised by algorithms. If we can’t trust banks then maybe we can’t trust fabs?

Trust is the foundation of all trade and business. Without trust, no deal can get done, no venture can be launched, no discussion can even begin. Trust has been shaken in individual businesses in recent years, but recently exposed financial scams have shaken confidence not just in one or a collection of companies but almost in the very value of money itself. Agencies gave high ratings to the long-term stability and value of CDO (collateralized debt obligations), which in the sober light of day are seen to have been illusions disguised by algorithms. If we can’t trust banks then maybe we can’t trust fabs?